1引言

视觉测量技术是以机器视觉技术为基础,融合电子技术、计算机技术、近景摄影测量技术、图像处理技术为一体的测量技术,其基本任务是以测量为目的,从图像信息出发计算三维空间中物体的几何信息。其中,图像处理技术是视觉测量系统中最重要的一部分,也是本文的研究重点。

传统的视觉测量系统主要是在 PC机上采用软件方式实现,由于其专用性不够高,因此处理速度较慢。近年来,基于 FPGA的SOPC技术的出现,使 FPGA高效的硬件并行信号处理能力和软件控制的灵活性完美的结合到一起。在SOPC系统中,对速度要求高的算法可以采用自定义硬件逻辑的方法实现;而用硬件难以实现的复杂算法以及控制流程可以在 Nios II核中以软件方式实现。因此基于SOPC技术的系统具有很好的实时性、灵活性以及可扩展性。设计者可以自由的进行软硬协同设计,并且可以在设计的各个阶段不受限制的修改设计而无需重新构建硬件平台。

本文所讨论的 SOPC系统是大尺寸三维视觉测量系统的一部分,以 PCI板卡的形式内嵌在PC机中。在整个大尺寸三维视觉测量系统中,采用数字相机从不同位置拍摄多幅图像,经过特征点提取、点中心的二维坐标计算、特征点匹配、三维拼接、面形拟合等步骤,得到被测物体的三维面形信息。点中心的计算精度直接影响测量精度,且其计算速度一直是系统的瓶颈之一。为提高处理速度和计算精度,采用SOPC系统完成特征点提取和点中心计算,其结果通过 PCI总线上传给 PC机,由其上的软件模块完成后续的计算和处理工作。

2 SOPC系统的总体设计方案

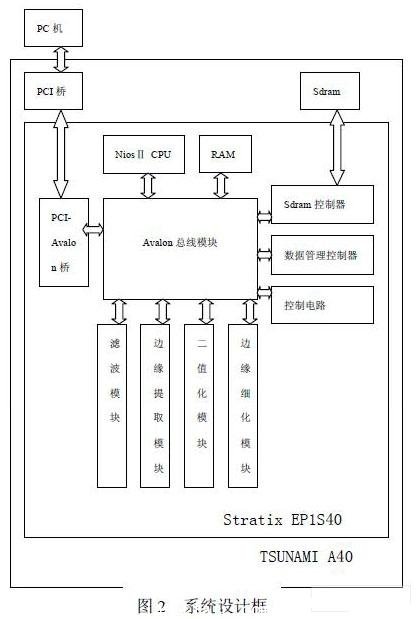

本系统采用加拿大 SBS公司的 TSUNAMI A40系列开发板,其核心的 FPGA模块是 Altera公司的 Stratix EP1S40芯片。

2.1 系统算法的基本原理

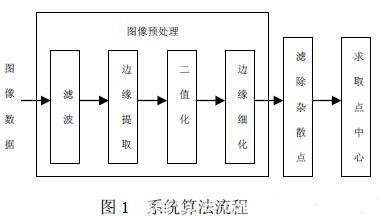

系统算法实现流程如图1所示。首先,针对本系统图像处理的要求与算法实现特点进行软硬件划分。图像预处理部分所需要处理的数据量比较大,但算法相对简单,可以通过FPGA自定义相应的 IP模块,采用硬件的方式实现;后续处理部分由于算法相对复杂,用硬件实现比较困难,而且其数据处理量不大,所以采用在Nios II软核中以软件的方式实现。最后编写系统控制软件对整个系统进行控制使软硬件协同工作。

2.2 系统硬件的设计方案

如图 2所示,本系统硬件开发板通过 PCI桥与 PC机相连,原始图片保存在 PC机中。 PCI-Avalon桥是 PC机与FPGA开发板的通信接口,图像数据经过 PCI-Avalon桥进入系统处理模块。Sdram管理控制器用来管理和控制Sdram中的数据存取。控制电路用来控制与协调各个外设的运行,实现状态控制与数据传输等基本操作,包括读取Sdram中保存的图像数据,控制图像处理各模块。 Sdram用来保存图像数据。原始图像数据最初由 PC机下载到 Sdram中,再通过Sdram管理控制器传输给各处理模块依次处理。处理后的图像数据仍然通过 Sdram管理控制器返回 Sdram中保存。最后通过PCI桥把最终图像返回到 PC机。

2.3 系统软件的设计

本系统的控制流程相对简单,因此在 Nios II软核中没有内嵌操作系统,而是通过IO操作调用中断的方式实现运行状态的控制、数据通信、协调外设等基本操作,控制系统各硬件模块,使系统软硬件协同工作。整个系统搭建成功之后,在PC机上编写应用程序对整个SOPC系统的运行进行控制。

3 系统算法的具体实现

3.1 滤波模块

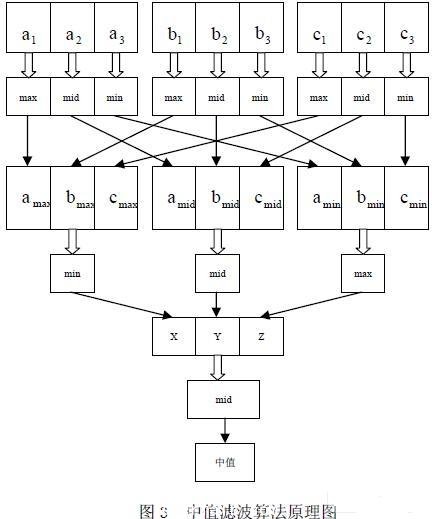

根据所采集到的图像的特点,本文采用3×3的模板实现中值滤波,这种方法不仅可以滤除图像中的噪声,而且可以将边缘信息很好的保留下来。一般求取中值的方法是采用取冒泡法排序,但这种算法并不适合硬件实现。考虑到硬件实现的特点和效率,本文采用了一种全新的求取中值的算法,其原理如图3所示。其中 max、mid、min分别表示三输入的最大值、中值和最小值比较器。最后经几轮比较后求得中值。

3.2 边缘提取模块及二值化模块

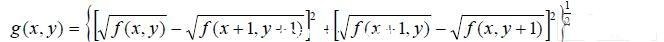

边缘提取采用 Roberts算子。 Roberts边缘检测算子利用局部差分算子寻找边缘,其计算由式 1给出。

由于待处理图像特征明显,采用经验阈值法对图像进行二值化,算法简单、实现方便。

3.3 边缘细化模块

本文的边缘是建立在二值化之后的,因此处理的图像都是二值化的,边缘非常清晰,不需要太复杂的算法。这里采用两个3×3模板作乘积,如图所示, X为待处理像素。如果模板乘积不为 0,于是中心象素为 1,反之为 0,即点的周围有灰度为0的象素,则保留此点,否则剔除。如此很容易得到二值化后点的单象素边缘。

3.4 后续处理部分

后续处理部分由于其数据处理量并不大且算法比较复杂,所以在本系统中,这部分算法在NiosⅡ中以软件的方法实现。由于篇幅所限,在此不作详细介绍。

4 系统测试结果的分析与总结

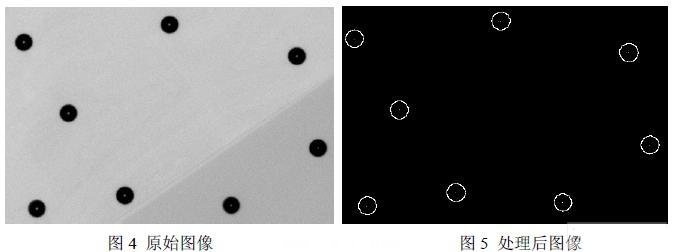

图 4为原始图像。图 5为处理后的最终图像,点中心已经标注如图所示。

经测试,本系统所有算法用 C语言在 PC机(配置: Pentium( R) 4 CPU 3.00GHz, 512MB内存)上实现,所需时间为 2'12",而本系统仅需 30",其中主要耗时为NiosII软件处理部分,系统的硬件算法部分所耗时间不到 1"。

本文作者创新点:一是采用 FPGA设计硬件模块实现图像预处理算法,这是视觉测量系统在处理效率上的创新;二是在系统中加入Nios II CPU,用以 FPGA难以实现的算法,从而使基于SOPC技术的视觉测量系统更具灵活性,这是视觉测量系统在灵活性方面的创新。基于以上两点创新设计的视觉测量系统兼顾了效率和灵活性,为视觉测量系统的设计和研究提供了一种新的思路。

转载请注明出处。

相关文章

相关文章

热门资讯

热门资讯

精彩导读

精彩导读

关注我们

关注我们